Product Summary

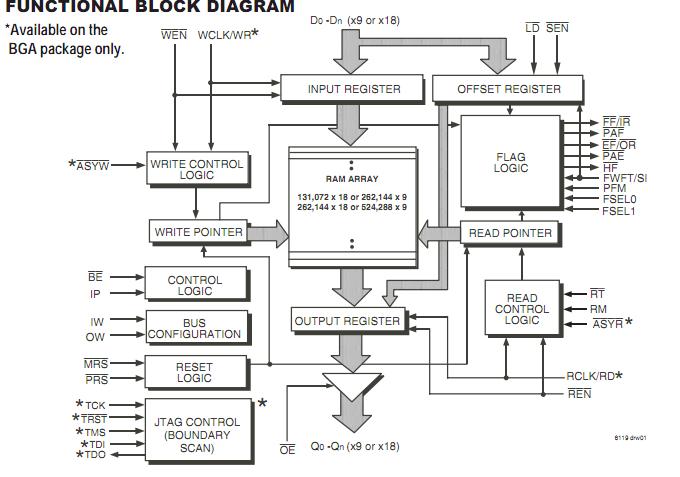

The IDT72V2103L15PF is an exceptionally deep, high speed, CMOS First-In-First-Out (FIFO) memory with clocked read and write controls and a flexible Bus-Matching x9/x18 data flow. The IDT72V2103L15PF has a data input port (Dn) and a data output port (Qn), both of which can assume either an 18-bit or a 9-bit width as determined by the state of external control pins Input Width (IW) and Output Width (OW) during the Master Reset cycle.

Parametrics

IDT72V2103L15PF absolute maximum ratings: (1)VTERM, Terminal Voltage with respect to GND:–0.5 to +4.5 V; (2)TSTG, Storage Temperature: –55 to +125℃; (3)IOUT, DC Output Current: –50 to +50 mA.

Features

IDT72V2103L15PF features: (1)Big-Endian/Little-Endian user selectable byte representation; (2)5V tolerant inputs; (3)Fixed, low first word latency; (4) Zero latency retransmit; (5)Auto power down minimizes standby power consumption; (6)Master Reset clears entire FIFO; (7)Partial Reset clears data, but retains programmable settings; (8)Empty, Full and Half-Full flags signal FIFO status; (9)Programmable Almost-Empty and Almost-Full flags, each flag can default to one of eight preselected offsets; (10)Selectable synchronous/asynchronous timing modes for Almost-Empty and Almost-Full flags.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

IDT72V2103L15PF |

|

IC FIFO SUPERSYNCII 15NS 80-TQFP |

Data Sheet |

|

|

||||||

|

IDT72V2103L15PF8 |

|

IC FIFO SUPERSYNCII 15NS 80-TQFP |

Data Sheet |

|

|

||||||

|

IDT72V2103L15PFG |

|

IC FIFO SUPERSYNCII 15NS 80-TQFP |

Data Sheet |

|

|

||||||

|

IDT72V2103L15PFG8 |

|

IC FIFO SUPERSYNCII 15NS 80-TQFP |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))