Product Summary

The TMS320C6415GLZ DSP composes the fixed-point DSP generation in the TMS320C6000 DSP platform. The TMS320C6415GLZ is based on the high-performance, advanced VelociTI very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making the C6205 an excellent choice for multichannel and multifunction applications. With performance of up to 1600 million instructions per second (MIPS) at a clock rate of 200 MHz, the TMS320C6415GLZ offers cost-effective solutions to high-performance DSP-programming challenges. The TMS320C6415GLZ DSP possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. This processor has 32 general-purpose registers of 32-bit word length and eight highly independent functional units. The eight functional units provide six arithmetic logic units (ALUs) for a high degree of parallelism and two 16-bit multipliers for a 32-bit result. The TMS320C6415GLZ can produce two multiply-accumulates (MACs) per cycle for a total of 400 million MACs per second (MMACS). It also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals.

Parametrics

TMS320C6415GLZ absolute maximum ratings: (1)Supply voltage ranges: CVDD: -0.3 V to 2.3 V, DVDD: -0.3 V to 4 V, (PCI), VIOP: -0.5 V to 5.5 V, (PCI), VDDP: -0.3 V to 4 V; (2)Input voltage ranges: (except PCI), VI: -0.3 V to 4 V, (PCI), VIP: -0.5 V to VIOP + 0.5 V; (3)Output voltage ranges: (except PCI), VO: -0.3 V to 4 V, (PCI), VOP: -0.5 V to VIOP + 0.5 V; (4)Operating case temperature range, TC: 0℃ to 90℃; (5)Storage temperature range, Tstg: -65℃ to 150℃.

Features

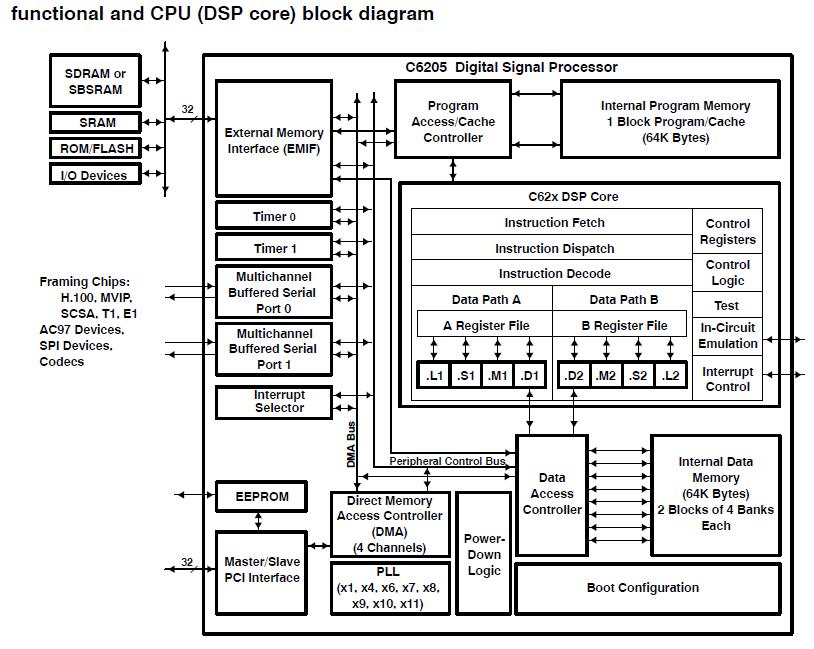

TMS320C6415GLZ features: (1)High-Performance Fixed-Point Digital Signal Processor (DSP)-TMS320C6205: 5-ns Instruction Cycle Time, 200-MHz Clock Rate, Eight 32-Bit Instructions/Cycle, 1600 MIPS; (2)VelociTI Advanced-Very-Long-Instruction-Word (VLIW) TMS320C62x DSP Core: Eight Highly Independent Functional; (3)Units: Six ALUs (32-/40-Bit), Two 16-Bit Multipliers (32-Bit Result), Load-Store Architecture With 32 32-Bit General-Purpose Registers, Instruction Packing Reduces Code Size, All Instructions Conditional; (4)Instruction Set Features: Byte-Addressable (8-, 16-, 32-Bit Data), 8-Bit Overflow Protection, Saturation, Bit-Field Extract, Set, Clear, Bit-Counting, Normalization.

Diagrams

|

TMS3112 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TMS3121 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TMS320 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TMS32010 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TMS320AV7110 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TMS320BC51PQ100 |

Texas Instruments |

Digital Signal Processors & Controllers (DSP, DSC) TMS320C51PQ - 132QFP - 100MHZ/BOOT CODE |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))